主板

时钟电路是计算机主板上的一个关键部分,负责生成和分发

时钟信号给主板上的各种组件,这些时钟信号确保所有组件能够同步工作,从而保证了计算机的稳定运行,下面我将详细介绍主板时钟电路图及其相关知识。,主板时钟电路的主要组成部分,

,1、

,1、

时钟发生器(Clock Generator):通常是一个晶振,用于产生基准时钟信号。,2、

时钟缓冲器(Clock Buffer):增强时钟信号的驱动能力,保证信号质量和传输距离。,3、

时钟分配网络(Clock Distribution Network):将时钟信号分配到主板上的各个部件。,4、

相位锁定环(Phase-Locked Loop, PLL):可调整时钟频率,以适应不同操作需求。,5、

倍频器(Multiplier):用来增加或减少时钟频率。,6、

电容器和电阻器:用以稳定电路和调节时钟信号。,时钟电路的作用与重要性,时钟电路的核心作用是提供一个精确且稳定的时钟信号源,这个信号是整个系统同步工作的基准,它对于处理器执行指令、内存存取数据、以及其他各种数据传输过程至关重要,如果时钟电路出现问题,可能会导致系统不稳定、性能下降甚至无法启动。,时钟电路图解析,

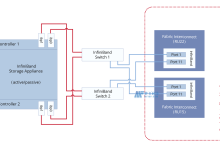

,为了深入理解主板时钟电路,我们需要查看一张详细的电路图,在电路图中,可以看到以下几个关键节点:,1、

,为了深入理解主板时钟电路,我们需要查看一张详细的电路图,在电路图中,可以看到以下几个关键节点:,1、

晶振连接:晶振通常连接到主板上的特定芯片,比如I/O芯片或者专用的超频芯片。,2、

PLL芯片:PLL芯片接收基础时钟信号,并输出一个或多个经过调整的时钟信号。,3、

时钟线路:从时钟发生器出发,通过缓冲器,再分布到各个需要时钟信号的组件。,4、

电源管理:电源管理单元会为时钟电路提供稳定的电源,以保证其正常工作。,故障排除与优化,当遇到主板时钟电路问题时,常见的诊断方法包括检查晶振是否起振、测量时钟信号的完整性以及检查PLL芯片是否正常工作,对时钟电路的优化可以通过选择更高质量的晶振、改进电源供电和使用更先进的PLL技术来实现。,相关问题与解答,Q1: 如何检测主板时钟电路是否正常?,

,A1: 可以使用示波器来检测晶振是否起振以及时钟信号的稳定性和准确性,还可以通过系统的性能表现和稳定性间接判断时钟电路是否正常。,Q2: 如果主板时钟电路出现故障,有什么表现?,A2: 时钟电路故障可能导致系统不稳定、频繁蓝屏、死机、启动困难或性能下降等问题。,Q3: 我能否自己更换主板上的晶振?,A3: 理论上可以,但需要一定的电子知识和动手能力,更换晶振时要确保新晶振的频率与旧的相匹配,并且正确安装,否则可能会损坏主板或其他组件。,Q4: 为什么高端主板会有多个时钟发生器?,A4: 高端主板通常会为不同的功能组件提供独立的时钟信号,以提高稳定性和超频潜力,使用多个时钟发生器可以减少信号干扰,并为每个组件提供最优化的时钟频率。,主板时钟电路是计算机中不可或缺的一部分,了解其工作原理和故障排除方法对于维修技术人员和电脑爱好者来说非常重要,通过对时钟电路图的分析,我们可以更好地理解系统的工作原理,并在必要时进行有效的故障排除和优化。,

,A1: 可以使用示波器来检测晶振是否起振以及时钟信号的稳定性和准确性,还可以通过系统的性能表现和稳定性间接判断时钟电路是否正常。,Q2: 如果主板时钟电路出现故障,有什么表现?,A2: 时钟电路故障可能导致系统不稳定、频繁蓝屏、死机、启动困难或性能下降等问题。,Q3: 我能否自己更换主板上的晶振?,A3: 理论上可以,但需要一定的电子知识和动手能力,更换晶振时要确保新晶振的频率与旧的相匹配,并且正确安装,否则可能会损坏主板或其他组件。,Q4: 为什么高端主板会有多个时钟发生器?,A4: 高端主板通常会为不同的功能组件提供独立的时钟信号,以提高稳定性和超频潜力,使用多个时钟发生器可以减少信号干扰,并为每个组件提供最优化的时钟频率。,主板时钟电路是计算机中不可或缺的一部分,了解其工作原理和故障排除方法对于维修技术人员和电脑爱好者来说非常重要,通过对时钟电路图的分析,我们可以更好地理解系统的工作原理,并在必要时进行有效的故障排除和优化。,

国外主机测评 - 国外VPS,国外服务器,国外云服务器,测评及优惠码

国外主机测评 - 国外VPS,国外服务器,国外云服务器,测评及优惠码