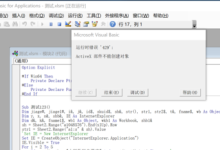

Allegro是一款由Cadence设计的高级 PCB(印刷电路板)布局工具,被广泛应用于电子设计自动化(EDA)领域,DRC(Design Rule Check)是电子设计过程中一个重要的步骤,用于检查PCB设计是否符合预定的设计规则,通常情况下,DRC会检查各种规则,例如线宽、线间距、孔径、层叠等。,当你提到“allegro等长DRC不报错”时,这意味着在设置等长规则后,DRC检查并未发现任何违反这些规则的地方,以下将详细解释为什么在allegro中进行等长DRC检查时可能不会出现错误。,等长规则是为了保证高速信号在传输过程中,各个信号线的长度差异保持在一定范围内,从而减少信号间的延迟差异,避免信号完整性问题,以下是一些可能导致等长DRC不报错的情形:,1、设计本身满足等长要求:在进行DRC检查之前,你已经仔细设置了等长规则,并且所有的信号线都严格遵循这些规则,这意味着所有的信号线对、组或者阶级都符合规定的长度公差,因此DRC检查不会报告任何错误。,2、等长规则的合理设置:等长规则可能已经根据实际的设计需求进行了合理设置,这可能包括适当的长度公差、等长组定义、忽略列表等,如果规则设置得当,DRC检查将不会因设计中的合法元素而报错。,长度公差:如果设置的长度公差足够大,即使在信号线布局过程中存在一些小的长度差异,也不会触发DRC错误。,等长组定义:正确地定义了等长组,确保所有需要保持等长的信号线都被包含在相应的组内。,忽略列表:合理配置忽略列表,可以排除某些特殊的信号线或区域,避免不必要的DRC错误。,3、高质量的布局:可能是因为PCB布局工程师的出色工作,确保了高速信号线的布局质量,合理的布线策略和技巧可以使得信号线长度自然满足等长要求,从而无需DRC介入。,4、DRC检查配置:在某些情况下,DRC的配置可能并未正确设置以检查等长规则,检查选项中可能遗漏了等长规则的勾选,或者等长规则并未被添加到DRC的规则集中。,5、缓冲区或修正措施:设计者可能已经采取了缓冲区或修正措施来确保等长要求得到满足,通过在布线中加入额外的长度或者调整某些走线,使得所有信号线长度都在规定范围内。,6、设计更新:在更新设计后,可能已经对不满足等长要求的部分进行了修正,这意味着之前的DRC错误已被识别并得到妥善处理。,7、软件版本或补丁:在某些情况下,软件的版本或已安装的补丁可能影响了DRC检查的行为,可能存在一些已知的bug被修复,或者某些功能得到了改进,从而使得等长DRC更加稳定和准确。,为了确保等长DRC的准确性,以下是一些建议:,确认等长规则的设置是否正确,并符合设计要求。,对等长组进行验证,确保所有必要的信号线都包含在内。,定期运行DRC检查,并仔细检查报告,确保没有遗漏的违规情况。,如果对DRC结果有疑问,可以尝试减小长度公差,看是否会有新的违规出现。,检查DRC设置,确保包含了所有设计规则,特别是等长规则。,保持对设计变更的跟踪,确保任何更新都不会影响等长要求。,使用最新版本的软件和补丁,以确保DRC检查的准确性和可靠性。,在allegro中执行等长DRC检查不报错,可能是由于多种原因造成的,设计者应该对自己的设计有深入的理解,并持续验证和优化DRC规则,以确保设计满足所有预定目标并符合制造要求。,

allegro等长drc不报错

版权声明:本文采用知识共享 署名4.0国际许可协议 [BY-NC-SA] 进行授权

文章名称:《allegro等长drc不报错》

文章链接:https://zhuji.vsping.com/460015.html

本站资源仅供个人学习交流,请于下载后24小时内删除,不允许用于商业用途,否则法律问题自行承担。

文章名称:《allegro等长drc不报错》

文章链接:https://zhuji.vsping.com/460015.html

本站资源仅供个人学习交流,请于下载后24小时内删除,不允许用于商业用途,否则法律问题自行承担。

国外主机测评 - 国外VPS,国外服务器,国外云服务器,测评及优惠码

国外主机测评 - 国外VPS,国外服务器,国外云服务器,测评及优惠码